# GLOBAL JOURNAL OF ENGINEERING SCIENCE AND RESEARCHES QCA DESIGN OF SRAM CELL USING REVERSIBLE ADDRESS DECODER

A.Benitto Bella<sup>\*1</sup> & Mr.P.N.Sundararajan M.E.,(Ph.D)<sup>2</sup> <sup>\*1</sup>ME (VLSI Design), PSNA CET, DINDIGUL

<sup>2</sup>Associate Professor, PSNA CET, DINDIGUL

## ABSTRACT

A memory unit is a gathering of capacity cells together with related circuits expected to change data all through the gadget. Memory cells which can be gotten to for data exchange to or from any coveted arbitrary area is called Random Access Memory (RAM). A decoder is an imperative part of memory, for address disentangling and encoding. The sizes of Complementary Metal Oxide Semiconductor (CMOS) transistor continue contracting to build the thickness on chip as per Moore's Law. The scaling influences the gadget execution because of requirements like warmth dissemination and power utilization. A Quantum spot Cellular Automaton (QCA) is another option to CMOS. It offers higher speed, bring down power utilization, and higher thickness. In non reversible doors some measure of energy misfortune is included. Enthusiasm for reversible rationale offers lessened warmth dispersal and expands the speed. It is another transistor less calculation in nanotechnology. In this venture propose a SRAM CELL configuration utilizing Feynman gate based decoder.It gives reversibility and territory minimization. QCA architect instrument has been utilized to approve the execution of reversible decoders.

**Keywords-** *Quantum Dot Cellular Automata (QCA), SRAM, Reversible Gates.*

## I. INTRODUCTION

The measure of Complementary Metal Oxide Semiconductor (CMOS) transistor keeps contracting to extend the thickness on chip according to Moore's Law [1]. In CMOS innovation, its component measure has decreased following a very long while [2]. Then again, several obstructions still exit. This has realized the speedy headway of nuclear plans on the nanoscale. QCA is one of the alternatives in nanotechnologies for FFT based gadget. It is depended upon to finish low zone and power usage and high trading speed. It has no voltage source and the position of electrons chooses the sensible qualities.

QCA cell involve four quantum dots masterminded in square example [3]. Each cell has two electrons which are liberated to entry to close-by spots. Electrons tend to keep farthest division between each other, they live corner to corner to each other as a result of equivalent electrostatic dreadful oblige between them. Cell has two special states, addressed by method of reasoning 0 and basis 1 [4].

Reversible circuits don't lose any information, and it can be make extraordinary yield vector from each data vector. Landauer showed that joules of imperativeness are made for each bit of information lost in view of non reversible figuring; essentialness dispersing would not by any means occur in reversible estimation. In Reversible entryway, there is composed mapping between the data and yield which is not the circumstance with customary premise. Using this reversible method of reasoning we can recuperate commitment from yield and the amount of data lines is equal to number of yield lines.

In this paper a gainful approach to manage examination and blueprint of SRAM with reversible address decoder using Quantum dot Cell Automata. This paper we use the larger part entryways is the fundamental fragment of the QCA circuit execution. The reversible SRAM circuit is laid out and propagation results are poor down using QCA originator instrument. The proposed structure of reversible SRAM required a decreased number of dominant part entryway capacities.

36

A powerful way to analyse and design of decoder with reversible NAND gate, which utilizing quantum dot cell automata in nanoscale. This paper we utilize the largest part gate is the principal segment of the QCA circuit execution. The proposed circuit is designed and simulated using quantum dot cell automata designer tool, this test system tool is more helpful for building an intricate info levels. The proposed structure required less number of greater part gate capacities contrasted with past structures.

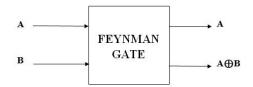

#### A. Feynman Gate

Feynman gate is a fundamental reversible gate. It has two sources of info and two yields [6]. To start with yield is same as the information and the other is XOR of contributions as appeared in Fig.2.1

Figure 2.1 Feynman Gate

Figure 2.2 Feynman gate circuit

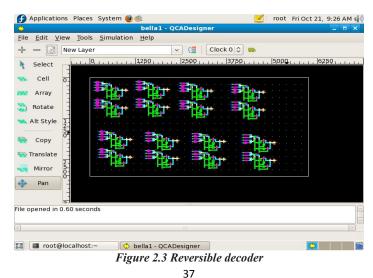

### B. Design a reversible decoder in QCA

Feynman Gate based 4 to 16 decoder can be designed in QCA. In this Reversible decoder area can be minimized and it offers a higher speed [7].

(C)Global Journal Of Engineering Science And Researches

## *[Bella*, 4(4): April 2017] DOI-10.5281/zenodo.557081 III. PROPOSED SRAM DESIGN

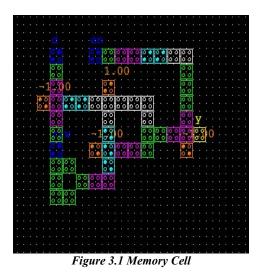

A 4-to-16 decoder addresses the 16 SRAM paths which has four tending to lines that can deliver up to 16 SRAM paths. Subsequent to choose the coveted SRAM path, as per the R/W line, 32 bits of information can be composed or perused. The read or write operation from one 32-bit SRAM path is connected as per the way delays and happens at the same clock. The R/W input decides the read or write method of the SRAM. An EN input interfaces with empower the decoder.

Decoders select every unit of memory cell having least deferral. The sensible action of the circuit is as per the following. At the point when the SRAM is chosen by the empower contribution of a decoder (EN), in the event that one SRAM path is chosen by four tending to decoder lines at the same time, then it will be chosen for R/W mode.SRAM will stay idle. If the R/W line is in a high state, written work happens. The R/W line and info information transport must achieve their separate memories amid one clock stage, on the grounds that the memory prepared to compose the info information is embedded in the meantime.

Figure 3.2 QCA Layout of SRAM1(using 2 to 4 reversible decoder)

38

ISSN 2348 - 8034 Impact Factor- 4.022

Figure 3.3 QCA layout of SRAM2 (using 4 to 16 decoder)

## **IV. SIMULATION RESULTS**

The output of the SRAM combined with reversible address decoder shown in fig 4. The total simulation time 0.51s.

| 😽 Simulati  | ion Result | 5    |                      | _          | _                 |            | _          | _                   | _          |              |                    |

|-------------|------------|------|----------------------|------------|-------------------|------------|------------|---------------------|------------|--------------|--------------------|

| X<br>Close  | Open       | Save | Print Previe         | w Print F  | (1)<br>Reset Zoom | Threshold  | s Decim    | al Binary           | Hex        |              |                    |

| Trace       | Vis        | 1    | max: 9.56e-00        | 1          |                   |            | <u> </u>   |                     |            |              |                    |

| ⊽ 🕶 y7      | [          |      | y-<br>min: -9.51e-00 |            |                   |            |            |                     |            |              |                    |

| y<br>₽ ₽ v5 | 7 [<br>[   |      |                      |            | 1 2000 1 3        | 099 1 4099 | 1 5090 1 6 | 17099               | 1 8000     | 9090   10900 | 111900 12900       |

| BE y        |            |      | y2                   |            |                   | $\square$  |            |                     |            |              |                    |

| ⊽ 🖙 y4      | [          |      |                      | 0( 0       | {°}               | {°}        | -{°}-      | -{°}-               | -{°}       | -{°}-        | 0                  |

| 🛃 y         |            |      |                      | 0-111 1090 | 1 2000 1 3        | 099 1 4099 | 1 5090 1 6 | 17090               | 1 8000     | 9090 1 10900 | 11000 12000        |

| ⊽y3<br>₩y   | 4 [        |      | max: 1.25e-003       |            |                   |            |            |                     |            |              |                    |

| ⊽ 💀 y2      |            |      | y:<br>min: -9.51e-00 |            |                   |            |            |                     |            |              |                    |

| У           |            |      |                      | 0-111 1099 | 1 2000 1 3        | PPQ   4PQQ | 1 5099 1 6 | P99 1 7999          | 1 8099 1   | 9000 1 10000 | 11000 12000        |

| ⊽y1<br>₽    | 1 [        |      | y1                   |            |                   |            |            |                     |            |              |                    |

| ▼ y0        |            |      |                      | ц)——( 1 )  | -{°}              | -{°}       | -{°}-      | -{°}-               | -{°}       | -{°}-        | - 00               |

| E y         |            |      | -                    | 9-111 1099 | 1 2099 1 3        | PP9 1 4P99 | 1 5099 1 6 | 17099               | 1 8099     | 9000 1 10000 | 11900 12900        |

| ⊽ 🕶 y6      | [          |      | max: 9.56e-00        |            |                   |            |            |                     |            |              |                    |

| a a         | 6 [        |      | y'<br>min: -9.51e-00 |            |                   |            |            |                     |            |              |                    |

| E b         | [          |      |                      | 0-111 1090 | 1 2000 1 3        | PP9 1 4P99 | 1 5099 1 6 | P99 1 7999          | 1 8099     | 9000 1 10000 | 111900 12900       |

| C           | [          |      | y0                   |            |                   |            |            |                     |            |              | 6                  |

| d           | [          |      |                      |            | ={°}              | -(°)       | -{°}-      | $\langle 1 \rangle$ | $\{\bot\}$ |              |                    |

| E b         | 1          |      |                      | 0+111 1099 | 1 2000 1 3        | pgg 1 4pgg | 1 5099 1 6 | P99 1 7999          | 1 8000     | 9000 1 10000 | 1110001 12000      |

| C C         | ſ          |      | max: 9.56e-00        |            |                   |            |            |                     |            |              | $\square$ $\Gamma$ |

| 📕 d         | ſ          |      | yl                   |            |                   |            |            |                     | -          |              |                    |

Figure 4.1 SRAM Output

## V. COMPARISON RESULTS

The simulation results Cell Count, Area are listed in Table I, Table and II.

| Table.1 Comparision Of Reversible Decoder |                       |                 |           |  |  |  |

|-------------------------------------------|-----------------------|-----------------|-----------|--|--|--|

| S.No.                                     | Reversible<br>Decoder | Number of cells | Area(μm)² |  |  |  |

| 1                                         | 2 to 4 decoder        | 808             | 2.32      |  |  |  |

| 2                                         | 4 to 16<br>decoder    | 3968            | 13.79     |  |  |  |

#### Table 2 Comparison Of Area

| S.No. | SRAM        | Number of | Area(µm <sup>2</sup> ) |  |

|-------|-------------|-----------|------------------------|--|

|       |             | cells     |                        |  |

| 1     | Memory cell | 51        | 0.06                   |  |

| 2     | SRAM1       | 1012      | 4.37                   |  |

| 2     | SRAM2       | 4784      | 14.37                  |  |

39

## *[Bella,* 4(4): April 2017] DOI-10.5281/zenodo.557081 VI. CONCLUSION

The design under consideration, i,e reversible decoder is said to be an area effective when designed with QCA rather than CMOS. There is an advantage of both low area and power at the same abstraction level, QCA can be seen as one of the promising technologies in near future. However there is still research going on in the inter disciplines of physical implementations and cost effective manufacturing process. High speed decoder is the essential components in fast SRAM[9]. The memory cell combined with the reversible address decoder implemented and results can be verified. The proposed SRAM which will be highly delay efficient design

## REFERENCES

- 1. D.Grier, "The innovation [Moore's law in semiconductor industry]." Computer, vol.39, pp.8-10, Feb 2006.

- 2. Steven C.Henderson, Eric w.Johnson, Jason R Janulis and P.Douglas, "Incorporating Standard CMOS Design process Methodologies into the QCA logic Design Process," IEEE Transactions on Nanotechnology, vol. 3, no. 1, March 2004.

- 3. P.Agrawal and B.Ghosh, "Innovative design methodologies in QCA," Int.J.Circuit Theory Appl., vol. 43, no.2, pp 253-262, 2015.

- 4. Heumpil Cho, Earl E. Swartzlander. "Adder and Multiplier Design in Quantum-Dot cellular Automata," IEEE Transaction on Computers, vol. 58, no. 6, June 2009

- 5. D.Balobas and N.Konofaos, "Desig of Low Power, High Performance 2-4 and 4-16 mixed logic Line Decoders," IEEE Transactions on Circuit and Systems II, 2015.

- 6. A.N.Bahar, S.Waheed, N.Hossain, "A new appoarch of presenting reversible logic gate in nanoscale, "Springer Plus, vol.4, pp.153-159, 2015.

- 7. Jadav Chandra Das, Debashis De and Tapatosh Sadhu, "A Novel Low Power Nanoscale Reversible Decoder Using Quantum Dot CellularAutomata For Nanocommunication," Third International Conference on Devices, Circuits and Systems (ICDCS'16), 2016.

- 8. M.Awais, M.Vacca, M.Graziano, "QCA check node implementation for LDPC decoders," IEEE Trans. Nanotechnol., vol. 12, no.3, pp. 368-377, May 2013.

- 9. Moein Kianpour and Reza Sabbaghi-Nadooshan, "A Novel Quantum-Dot Cellular Automata X-bit x 32-bit SRAM," IEEE Transactions on Very Large Scale Integration(VLSI) Systems vol. 23, no. 3, March 2016.

- 10. K.S.Mahalakshmi, Hajeri Jayashree H.V, Vinod Kumar Agarwal, "Performance Estimation of Conventional Reversible Logic Circuits Using QCA Implementation Platform", International Confrence on Circuit , Power and Computing Technologies [ICCPCT], 2016.